#### DEVICE PERFORMANCE SPECIFICATION

Revision 2.0 MTD/PS-0719

January 25, 2006

KODAK KAI-4021 IMAGE SENSOR

2048(H) X 2048(V) INTERLINE CCD IMAGE SENSOR

## **TABLE OF CONTENTS**

| Summary Specification                                     | 5  |

|-----------------------------------------------------------|----|

| Device Description                                        | 6  |

| Architecture                                              | 6  |

| Pixel                                                     | 7  |

| Vertical to Horizontal Tranfer                            | 8  |

| Horizontal Register to Floating Diffusion                 | 9  |

| Horizontal Register Split                                 | 10 |

| Single Output Operation                                   | 10 |

| Dual Output Operation                                     | 10 |

| Output                                                    | 11 |

| ESD Protection                                            | 13 |

| Pin Description and Physical Orientation                  | 14 |

| Performance                                               | 15 |

| Power - Estimated                                         | 15 |

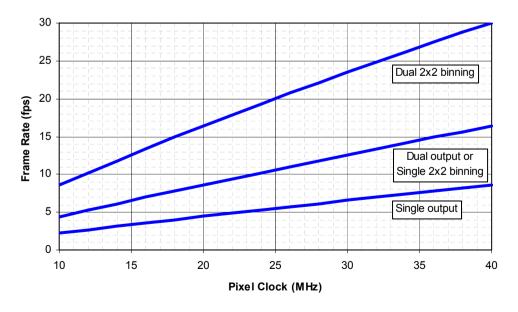

| Frame Rates                                               | 15 |

| Imaging Performance                                       | 16 |

| Imaging Performance Operational Conditions                | 16 |

| Imaging Performance Specifications                        | 16 |

| Defect Definitions                                        | 18 |

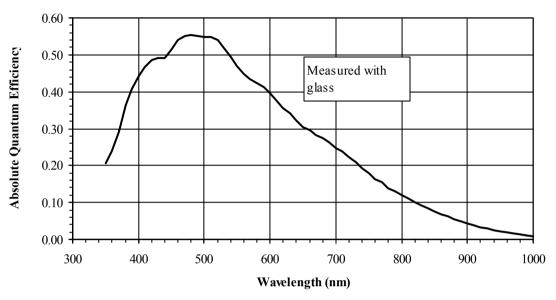

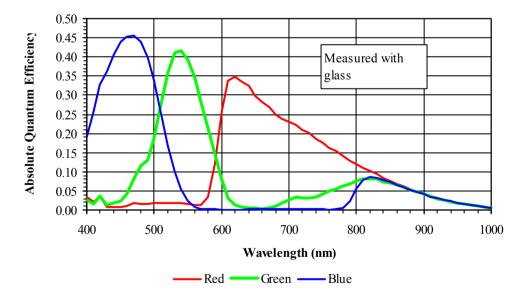

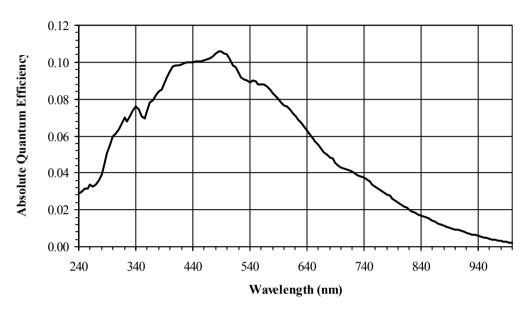

| Quantum Efficiency                                        | 19 |

| Angular Quantum Efficiency                                | 20 |

| Dark Current versus Temperature                           | 21 |

| Test Definitions                                          |    |

| Test Regions of Interest                                  | 22 |

| OverClocking                                              |    |

| Tests                                                     |    |

| Operation                                                 |    |

| Maximum Ratings                                           |    |

| Maximum Voltage Ratings Between Pins                      |    |

| DC Bias Operating Conditions                              |    |

| AC Operating Conditions                                   |    |

| Clock Levels                                              |    |

| Clock Line Capacitances                                   |    |

| Timing Requirements                                       |    |

| Timing Modes                                              |    |

| Progressive Scan                                          |    |

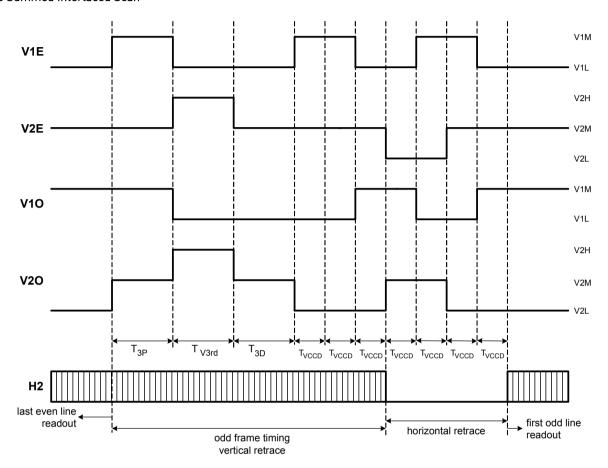

| Summed Interlaced Scan                                    |    |

| Non-Summed Interlaced Scan                                |    |

| Frame Timing                                              |    |

| Frame Timing without Binning – Progressive Scam           |    |

| Frame Timing for Vertical Binning by 2 – Progressive Scan |    |

| Frame Timing Non-Summed Interlaced Scan                   |    |

| Frame Timing Summed Interlaced Scan                       |    |

| Frame Timing Edge Alignment                               |    |

| Line Timing                                               |    |

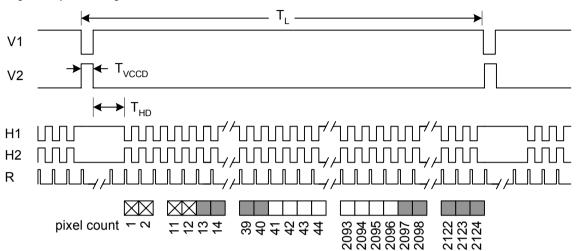

| Line Timing Single Output – Progressive Scan              | 38 |

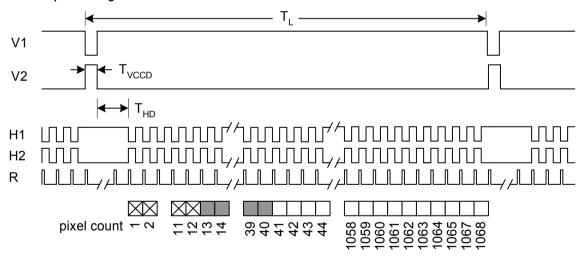

| Line Timing Dual Output – Progressive Scan           | 38 |

|------------------------------------------------------|----|

| Line Timing Vertical Binning by 2 – Progressive Scan |    |

| Line Timing Detail - Progressive Scan                |    |

| Line Timing Binning by 2 Detail – Progressive Scan   | 40 |

| Line Timing Interlaced Modes                         | 41 |

| Line Timing Edge Alignment                           | 42 |

| Pixel Timing                                         | 43 |

| Pixel Timing Detail                                  | 43 |

| Fast Line Dump Timing                                | 44 |

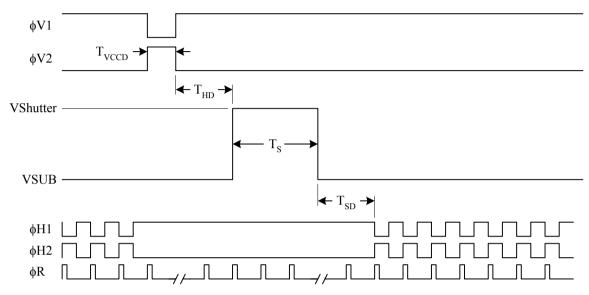

| Electronic Shutter                                   |    |

| Electronic Shutter Line Timing                       | 45 |

| Electronic Shutter – Integration Time Definition     | 45 |

| Electronic Shutter Description                       | 46 |

| Large Signal Output                                  | 46 |

| Storage and Handling                                 | 47 |

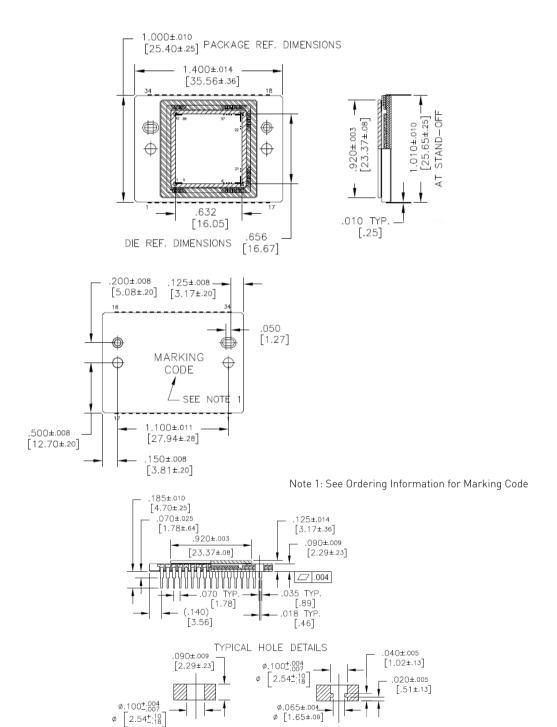

| Mechanical Drawings                                  | 48 |

| Package                                              | 48 |

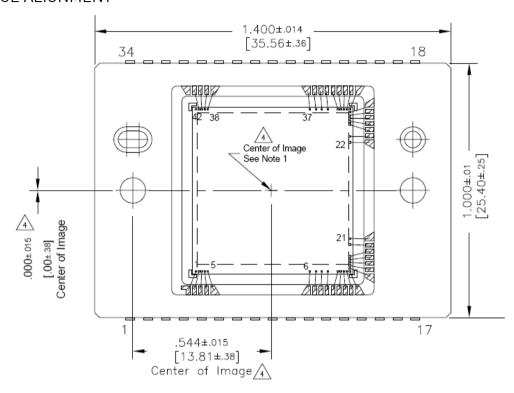

| Die to Package Alignment                             | 49 |

| Glass                                                |    |

| Glass Transmission                                   |    |

| Quality Assurance and Reliability                    |    |

| Ordering Information                                 |    |

| Revision Changes                                     | 54 |

# TABLE OF FIGURES

| Figure 1: Sensor Architecture                                    | 6  |

|------------------------------------------------------------------|----|

| Figure 2: Pixel Architecture                                     |    |

| Figure 3: Vertical to Horizontal Transfer Architecture           | 8  |

| Figure 4: Horizontal Register to Floating Diffusion Architecture |    |

| Figure 5: Horizontal Register                                    |    |

| Figure 6: Output Architecture                                    |    |

| Figure 7: ESD Protection                                         |    |

| Figure 8: Power                                                  |    |

| Figure 9: Frame Rates                                            |    |

| Figure 10: Monochrome Quantum Efficiency                         |    |

| Figure 11: Color Quantum Efficiency                              |    |

| Figure 12: Ultraviolet Quantum Efficiency                        |    |

| Figure 13: Angular Quantum Efficiency                            |    |

| Figure 14: Dark Current versus Temperature                       |    |

| Figure 15: Overclock Regions of Interest                         |    |

| Figure 16: Output Amplifier                                      |    |

| Figure 17: Clock Line Capacitances                               |    |

| Figure 18: Framing Timing without Binning                        |    |

| Figure 19: Frame Timing for Vertical Binning by 2                |    |

| Figure 20: Non-Summed Interlaced Scan Even Frame Timing          |    |

| Figure 21: Non-Summed Interlaced Scan Odd Frame Timing           |    |

| Figure 22: Summed Interlaced Scan Even Frame Timing              |    |

| Figure 23: Summed Interlaced Scan Odd Frame Timing               |    |

| Figure 24: Frame Timing Edge Alignment                           |    |

| Figure 25: Line Timing Single Output                             |    |

| Figure 26: Line Timing Dual Output                               |    |

| Figure 27: Line Timing Vertical Binning by 2                     |    |

| Figure 28: Line Timing Detail                                    |    |

| Figure 29: Line Timing by 2 Detail                               |    |

| Figure 30: Line Timing Interlaced Modes                          |    |

| Figure 31: Line Timing Edge Alignment                            |    |

| Figure 32: Pixel Timing                                          |    |

| Figure 33: Pixel Timing Detail                                   |    |

| Figure 34: Fast Line Dump Timing                                 |    |

| Figure 35: Electronic Shutter Line Timing                        |    |

| Figure 36: Integration Time Definition                           |    |

| Figure 37: Package Drawing                                       |    |

| Figure 38: Die to Package Alignment                              |    |

| Figure 39: Glass Drawing                                         |    |

| Figure 40: Glass Transmission                                    | 51 |

### SUMMARY SPECIFICATION

### KODAK KAI-4021 IMAGE SENSOR

### 2048 (H) X 2048 (V) INTERLINE TRANSFER PROGRESSIVE SCAN CCD

### **DESCRIPTION**

The Kodak KAI-4021 Image Sensor is a high-performance 4-million pixel sensor designed for a wide range of medical, scientific and machine vision applications. The 7.4  $\mu$ m square pixels with microlenses provide high sensitivity and the large full well capacity results in high dynamic range. The two high-speed outputs and binning capabilities allow for 16-50 frames per second (fps) video rate for the progressively scanned images. The vertical overflow drain structure provides antiblooming protection and enables electronic shuttering for precise exposure control. Other features include low dark current, negligible lag and low smear.

#### **FEATURES**

- High resolution

- High sensitivity

- High dynamic range

- Low noise architecture

- High frame rate

- Binning capability for higher frame rate

- Electronic shutter

### **APPLICATIONS**

Industrial inspection

| Parameter                    | Value                 |

|------------------------------|-----------------------|

| Architecture                 | Interline CCD;        |

| Architecture                 | Progressive Scan      |

| Total Number of Pixels       | 2112 (H) x 2072 (V) = |

| Total Number of Pixets       | approx. 4.38M         |

| Number of Effective Pixels   | 2056 (H) x 2062 (V) = |

| Nulliber of Effective Fixets | approx. 4.24M         |

| Number of Active Pixels      | 2048 (H) x 2048 (V) = |

| Number of Active Lixets      | approx. 4.19M         |

| Number of Outputs            | 1 or 2                |

| Pixel Size                   | 7.4μm (H) x 7.4μm (V) |

| Imager Size                  | 21.43mm (diagonal)    |

| Chip Size                    | 16.67mm (H) x         |

| Offip Size                   | 16.05mm (V)           |

| Aspect Ratio                 | 1:1                   |

| Saturation Signal            | 40,000 e              |

| Peak Quantum Efficiency      | 55%                   |

| (KAI-4021M)                  | 33 /0                 |

| Peak Quantum Efficiency      | 45%, 42%, 35%         |

| (KAI-4021CM) BGR             | , ,                   |

| Output Sensitivity           | 31 μV/e               |

| Total System Noise           | 25 e                  |

| (at 40MHZ)                   | 200                   |

| Total System Noise           | 12 e                  |

| (at 20MHz)                   |                       |

| Dark Current                 | < 0.5 nA/cm2          |

| Dark Current Doubling        | 7°C                   |

| Temperature                  | , , ,                 |

| Dynamic Range                | 60 dB                 |

| Charge Transfer Efficiency   | > 0.99999             |

| Blooming Suppression         | 300X                  |

| Smear                        | 80 dB                 |

| Image Lag                    | <10 e                 |

| Maximum Data Rate            | 40 MHz                |

All parameters above are specified at T = 40°C

#### **DEVICE DESCRIPTION**

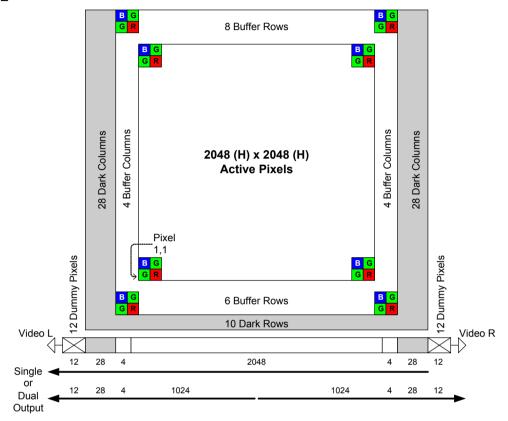

### **ARCHITECTURE**

Figure 1: Sensor Architecture

There are 10 light shielded rows followed 2062 photoactive rows. The first 6 and the last 8 photoactive rows are buffer rows giving a total of 2048 lines of image data.

In the single output mode all pixels are clocked out of the Video L output in the lower left corner of the sensor. The first 12 empty pixels of each line do not receive charge from the vertical shift register. The next 28 pixels receive charge from the left light-shielded edge followed by 2056 photo-sensitive pixels and finally 28 more light shielded pixels from the right edge of the sensor. The first and last 4 photosensitive pixels are buffer pixels giving a total of 2048 pixels of image data.

In the dual output mode the clocking of the right half of the horizontal CCD is reversed. The left half of the image is clocked out Video L and the right half of the image is clocked out Video R. Each row consists of 12 empty pixels followed by 28 light shielded pixels followed by 1028 photosensitive pixels. When reconstructing the image, data from Video R will have to be reversed in a line buffer and appended to the Video L data.

There are no dark reference rows at the top and 10 dark rows at the bottom of the image sensor. The 10 dark rows are not entirely dark and so should not be used for a dark reference level. Use the 28 dark columns on the left or right side of the image sensor as a dark reference.

Of the 28 dark columns, the first and last dark columns should not be used for determining the zero signal level. Some light does leak into the first and last dark columns. Only use the center 26 columns of the 28 column dark reference..

### **PIXEL**

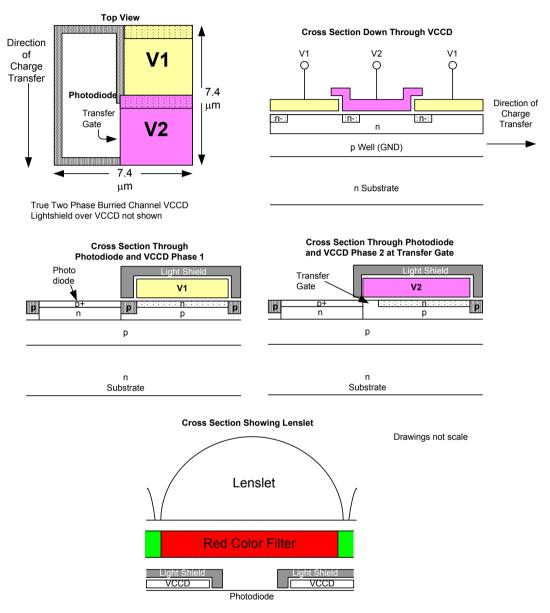

Figure 2: Pixel Architecture

An electronic representation of an image is formed when incident photons falling on the sensor plane create electron-hole pairs within the individual silicon photodiodes. These photoelectrons are collected locally by the formation of potential wells at each photosite. Below photodiode saturation, the number of

photoelectrons collected at each pixel is linearly dependant upon light level and exposure time and non-linearly dependant on wavelength. When the photodiodes charge capacity is reached, excess electrons are discharged into the substrate to prevent blooming.

### VERTICAL TO HORIZONTAL TRANFER

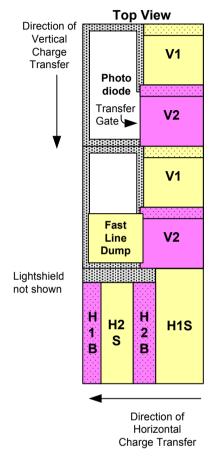

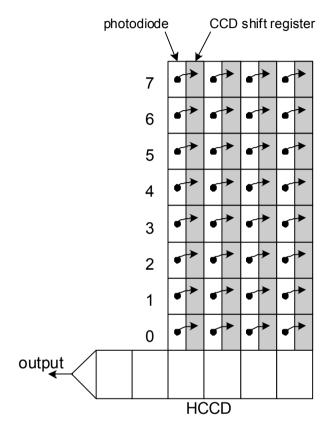

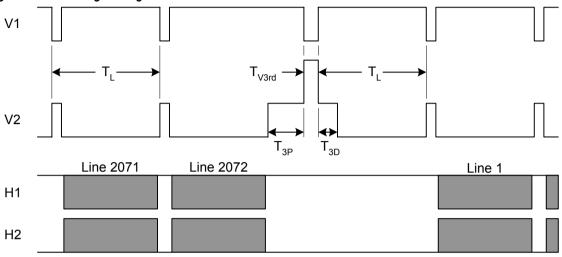

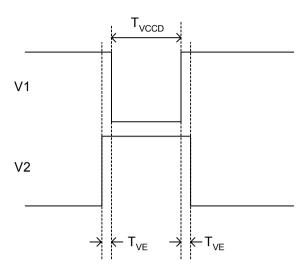

Figure 3: Vertical to Horizontal Transfer Architecture

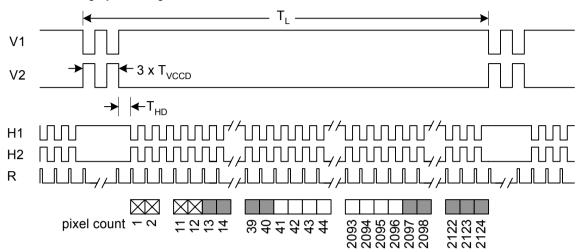

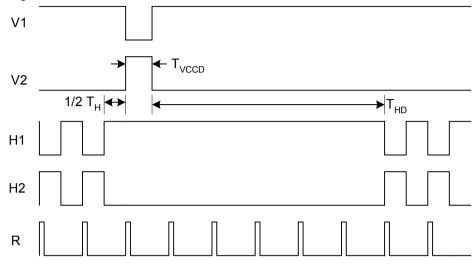

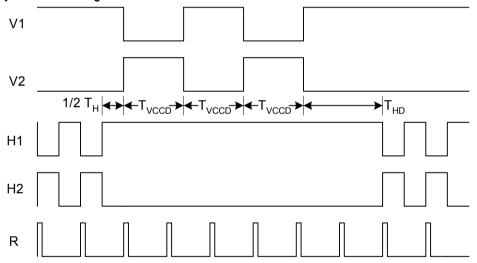

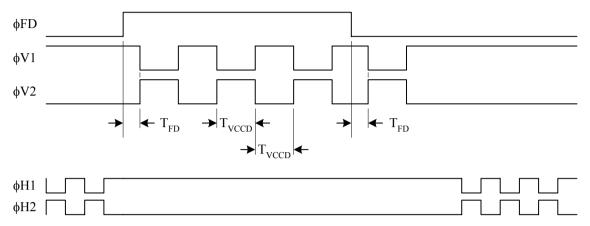

When the V1 and V2 timing inputs are pulsed, charge in every pixel of the VCCD is shifted one row towards the HCCD. The last row next to the HCCD is shifted into the HCCD. When the VCCD is shifted, the timing signals to the HCCD must be stopped. H1 must be stopped in the high state and H2 must be stopped in the low state. The HCCD clocking may begin THD  $\mu s$  after the falling edge of the V1 and V2 pulse.

Charge is transferred from the last vertical CCD phase into the H1S horizontal CCD phase. Refer to Figure 28 for an example of timing that accomplishes the vertical to horizontal transfer of charge.

If the fast line dump is held at the high level (FDH) during a vertical to horizontal transfer, then the entire line is removed and not transferred into the horizontal register.

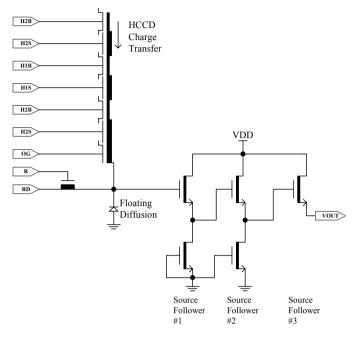

### HORIZONTAL REGISTER TO FLOATING DIFFUSION

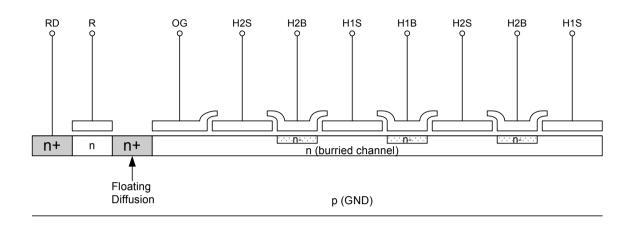

Figure 4: Horizontal Register to Floating Diffusion Architecture

n (SUB)

The HCCD has a total of 2124 pixels. The 2112 vertical shift registers (columns) are shifted into the center 2112 pixels of the HCCD. There are 12 pixels at both ends of the HCCD, which receive no charge from a vertical shift register. The first 12 clock cycles of the HCCD will be empty pixels (containing no electrons). The next 28 clock cycles will contain only electrons generated by dark current in the VCCD and photodiodes. The next 2056 clock cycles will contain photo-electrons (image data). Finally, the last 28 clock cycles will contain only electrons generated by dark current in the VCCD and photodiodes. Of the 28 dark columns, the first and last dark columns should not be used for determining the zero signal level. Some light does leak into the first and last dark columns. Only use the center 26 columns of the 28 column dark reference

When the HCCD is shifting valid image data, the timing inputs to the electronic shutter (SUB), VCCD (V1, V2), and fast line dump (FD) should be not be pulsed. This prevents unwanted noise from being introduced. The HCCD is a type of charge coupled device known as a pseudo-two phase CCD. This type of CCD has the ability to shift charge in two directions. This allows the entire image to be shifted out to the video L output, or to the video R output (left/right image reversal). The HCCD is split into two equal halves of 1068 pixels each. When operating the sensor in single output mode the two halves of the HCCD are shifted in the same direction. When operating the sensor in dual output mode the two halves of the HCCD are shifted in opposite directions. The direction of charge transfer in each half is controlled by the H1BL, H2BL, H1BR, and H2BR timing inputs.

### HORIZONTAL REGISTER SPLIT

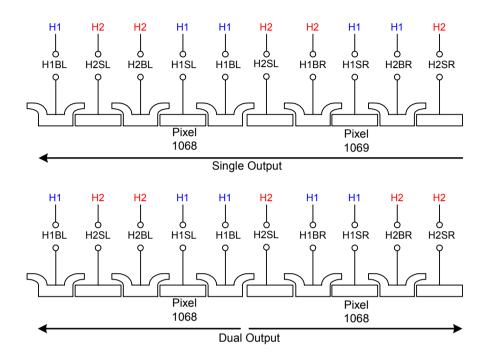

Figure 5: Horizontal Register

### Single Output Operation

When operating the sensor in single output mode all pixels of the image sensor will be shifted out the Video L output (pin 12). To conserve power and lower heat generation the output amplifier for Video R may be turned off by connecting VDDR (pin 24) and VOUTR (pin 23) to GND (zero volts).

The H1 timing from the timing diagrams should be applied to H1SL, H1BL, H1SR, H2BR, and the H2 timing should be applied to H2SL, H2BL, H2SR, and H1BR. In other words, the clock driver generating the H1 timing should be connected to pins 16, 15, 19, and 21. The clock driver generating the H2 timing should be connected to pins 17, 14, 18, and 20. The horizontal CCD should be clocked for 12 empty pixels plus 28 light shielded pixels plus 2056 photoactive pixels plus 28 light shielded pixels for a total of 2124 pixels.

### **Dual Output Operation**

In dual output mode the connections to the H1BR and H2BR pins are swapped from the single output mode to change the direction of charge transfer of the right side horizontal shift register. In dual output mode both VDDL and VDDR (pins 11, 24) should be connected to 15 V. The H1 timing from the timing diagrams should be applied to H1SL, H1BL, H1SR, H1BR, and the H2 timing should be applied to H2SL, H2BL, H2SR, and H2BR. The clock driver generating the H1 timing should be connected to pins 16, 15, 19, and 20. The clock driver generating the H2 timing should be connected to pins 17, 14, 18, and 21. The horizontal CCD should be clocked for 12 empty pixels plus 28 light shielded pixels plus 1028 photoactive pixels for a total of 1068 pixels. If the camera is to have the option of dual or single output mode, the clock driver signals sent to H1BR and H2BR may be swapped by using a relay. Another alternative is to have two extra clock drivers for H1BR and H2BR and invert the signals in the timing logic generator. If two extra clock drivers are used, care must be taken to ensure the rising and falling edges of the H1BR and H2BR clocks occur at the same time (within 3ns) as the other HCCD clocks.

### OUTPUT

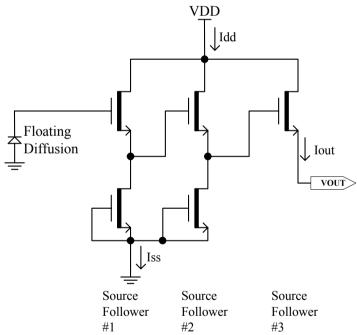

Figure 6: Output Architecture

Charge packets contained in the horizontal register are dumped pixel by pixel onto the floating diffusion (fd) output node whose potential varies linearly with the quantity of charge in each packet. The amount of potential charge is determined by the expression  $\Delta V fd = \Delta Q/Cfd$ . A three-stage source-follower amplifier is used to buffer this signal voltage off chip with slightly less than unity gain. The translation from the charge domain to the voltage domain is quantified by the output sensitivity or charge to voltage conversion in terms of microvolts per electron ( $\mu V/e^-$ ). After the signal has been sampled off chip, the reset clock (R) removes the charge from the floating diffusion and resets its potential to the reset drain voltage (RD).

When the image sensor is operated in the binned or summed interlaced modes there will be more than 20,000 electrons in the output signal. The image sensor is designed with a 31 $\mu$ V/e charge to voltage conversion on the output. This means a full signal of 20,000 electrons will produce a 640 mV change on the output amplifier. The output amplifier was designed to handle an output swing of 640 mV at a pixel rate of 40 MHz. If 40,000 electron charge packets are generated in the binned or summed interlaced modes then the output

amplifier output will have to swing 1280 mV. The output amplifier does not have enough bandwidth (slew rate) to handle 1280 mV at 40 MHz. Hence, the pixel rate will have to be reduced to 20 MHz if the full dynamic range of 40,000 electrons is desired.

The charge handling capacity of the output amplifier is also set by the reset clock voltage levels. The reset clock driver circuit is very simple, if an amplitude of 5 V is used. But the 5V amplitude restricts the output amplifier charge capacity to 20,000 electrons. If the full dynamic range of 40,000 electrons is desired then the reset clock amplitude will have to be increased to 7V.

If you only want a maximum signal of 20,000 electrons in binned or summed interlaced modes, then a 40 MHz pixel rate with a 5 V reset clock may be used. The output of the amplifier will be unpredictable above 20,000 electrons so be sure to set the maximum input signal level of your analog to digital converter to the equivalent of 20,000 electrons (640mV).

The following table summarizes the previous explanation on the output amplifier's operation. Certain trade-offs can be made based on application needs such as Dynamic Range or Pixel frequency.

| Pixel Freq.<br>(MHz) | Reset Clock<br>Amplitude (V) | Output Gate<br>(V) | Saturation<br>Signal (mV) | Saturation<br>Signal (ke <sup>-</sup> ) | Dynamic<br>Range (dB) | Notes |

|----------------------|------------------------------|--------------------|---------------------------|-----------------------------------------|-----------------------|-------|

| 40                   | 5                            | -2                 | 640                       | 20                                      | 60                    |       |

| 20                   | 5                            | -2                 | 640                       | 20                                      | 64                    |       |

| 20                   | 7                            | -3                 | 1280                      | 40                                      | 70                    |       |

| 20                   | 7                            | -3                 | 2560                      | 80                                      | 76                    | 1     |

Notes:

<sup>1. 80,000</sup> electrons achievable in summed interlaced or binning modes.

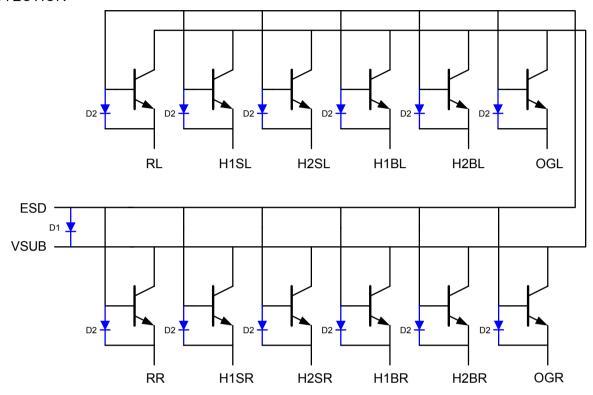

### **ESD PROTECTION**

Figure 7: ESD Protection

The ESD protection on the KAI-4021 is implemented using bipolar transistors. The substrate (VSUB) forms the common collector of all the ESD protection transistors. The ESD pin is the common base of all the ESD protection transistors. Each protected pin is connected to a separate emitter as shown in Figure 7: ESD Protection.

The ESD circuit turns on if the base-emitter junction voltage exceeds 17 V. Care must be taken while operating the image sensor, especially during the power on sequence, to not forward bias the base-emitter or base-collector junctions. If it is possible for the camera

power up sequence to forward bias these junctions then diodes D1 and D2 should be added to protect the image sensor. Put one diode D1 between the ESD and VSUB pins. Put one diode D2 on each pin that may forward bias the base-emitter junction. The diodes will prevent large currents from flowing through the image sensor. Note that external diodes D1 and D2 are optional and are only needed if it is possible to forward bias any of the junctions.

Note that diodes D1 and D2 are added external to the KAI-4021 CCD.

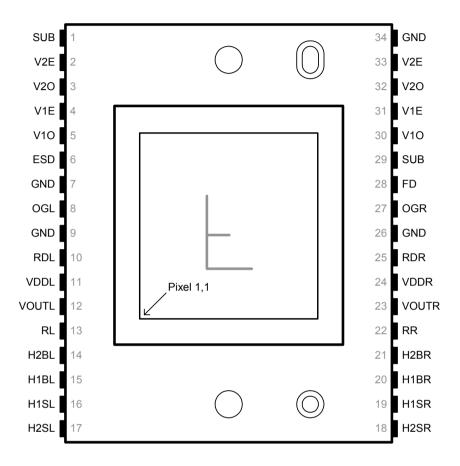

## PIN DESCRIPTION AND PHYSICAL ORIENTATION

| Pin | Name  | Description                   |

|-----|-------|-------------------------------|

| 1   | SUB   | Substrate                     |

| 2   | V2E   | Vertical Clock, Phase 2, Even |

| 3   | V20   | Vertical Clock, Phase 2, Odd  |

| 4   | V1E   | Vertical Clock, Phase 1, Even |

| 5   | V10   | Vertical Clock, Phase 1, Odd  |

| 6   | ESD   | ESD                           |

| 7   | GND   | Ground                        |

| 8   | OGL   | Output Gate, Left             |

| 9   | GND   | Ground                        |

| 10  | RDL   | Reset Drain, Left             |

| 11  | VDDL  | Vdd, Left                     |

| 12  | VOUTL | Video Output, Left            |

| 13  | RL    | Reset Gate, Left              |

| 14  | H2BL  | H2 Barrier, Left              |

| 15  | H1BL  | H1 Barrier, Left              |

| 16  | H1SL  | H1 Storage, Left              |

| 17  | H2SL  | H2 Storage, Left              |

The pins are on a 0.070" spacing

| Pin | Name  | Description                   |

|-----|-------|-------------------------------|

| 34  | GND   | Ground                        |

| 33  | V2E   | Vertical Clock, Phase 2, Even |

| 32  | V20   | Vertical Clock, Phase 2, Odd  |

| 31  | V1E   | Vertical Clock, Phase 1, Even |

| 30  | V10   | Vertical Clock, Phase 1, Odd  |

| 29  | SUB   | Substrate                     |

| 28  | FD    | Fast Line Dump Gate           |

| 27  | OGR   | Output Gate. Right            |

| 26  | GND   | Ground                        |

| 25  | RDR   | Reset Drain, Right            |

| 24  | VDDR  | Vdd, Right                    |

| 23  | VOUTR | Video Output. Right           |

| 22  | RR    | Reset Gate, Right             |

| 21  | H2BR  | H2 Barrier, Right             |

| 20  | H1BR  | H1 Barrier, Right             |

| 19  | H1SR  | H1 Storage, Right             |

| 18  | H2SR  | H2 Storage, Right             |

## **PERFORMANCE**

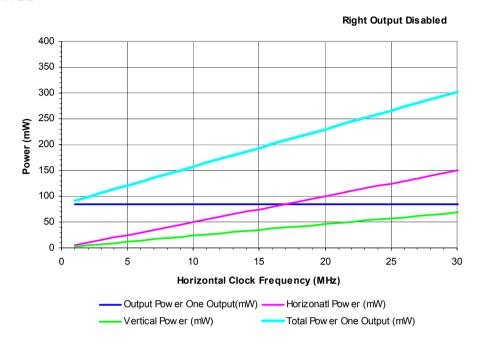

## **POWER - ESTIMATED**

Figure 8: Power

## FRAME RATES

Figure 9: Frame Rates

### IMAGING PERFORMANCE

### **Imaging Performance Operational Conditions**

Unless otherwise noted, the Imaging Performance Specifications are measured using the following conditions.

| Description                | Condition                                                                   | Notes |

|----------------------------|-----------------------------------------------------------------------------|-------|

| Frame Time                 | 538 msec                                                                    | 1     |

| Horizontal Clock Frequency | 10 MHz                                                                      |       |

| Light Source               | Continuous red, green and blue illumination centered at 450, 530 and 650 nm | 2,3   |

| Operation                  | Nominal operating voltages and timing                                       |       |

#### Notes:

- 1. Electronic shutter is not used. Integration time equals frame time.

- 2. LEDs used: Blue: Nichia NLPB500, Green: Nichia NSPG500S and Red: HP HLMP-8115.

- 3. For monochrome sensor, only green LED used.

## **Imaging Performance Specifications**

KA<u>I-4021M</u> and KAI-4021CM

| Description                                   | Symbol            | Min.    | Nom. | Max. | Units              | Samp-<br>ling<br>Plan | Tempera-<br>ture<br>Tested At<br>(°C) | Notes | Test |

|-----------------------------------------------|-------------------|---------|------|------|--------------------|-----------------------|---------------------------------------|-------|------|

| Dark Center Non-Uniformity                    |                   | n/a     | n/a  | 2    | mVrms              | Die                   | 27, 40                                |       | 1    |

| Dark Global Non-Uniformity                    |                   | n/a     | n/a  | 5.0  | mVpp               | Die                   | 27, 40                                |       | 2    |

| Global Non-Uniformity                         |                   | n/a     | 2.5  | 5.0  | %rms               | Die                   | 27, 40                                | 1     | 3    |

| Global Peak to Peak Non-<br>Uniformity        | PRNU              | n/a     | 10   | 20   | %рр                | Die                   | 27, 40                                | 1     | 4    |

| Center Non-Uniformity                         |                   | n/a     | 1.0  | 2.0  | %rms               | Die                   | 27, 40                                | 1     | 5    |

| Maximum Photoresponse Nonlinearity            | NL                | n/a     | 2    |      | %                  | Design                |                                       | 2, 3  |      |

| Maximum Gain Difference<br>Between Outputs    | ΔG                | n/a     | 10   |      | %                  | Design                |                                       | 2, 3  |      |

| Max. Signal Error due to<br>Nonlinearity Dif. | ΔNL               | n/a     | 1    |      | %                  | Design                |                                       | 2, 3  |      |

| Horizontal CCD Charge<br>Capacity             | HNe               |         | 100  |      | ke⁻                | Design                |                                       |       |      |

| Vertical CCD Charge Capacity                  | VNe               | 50      | 60   |      | ke⁻                | Die                   |                                       |       |      |

| Photodiode Charge Capacity                    | PNe               | 38      | 40   |      | ke⁻                | Die                   |                                       |       |      |

| Horizontal CCD Charge<br>Transfer Efficiency  | HCTE              | 0.99999 |      | n/a  |                    | Design                |                                       |       |      |

| Vertical CCD Charge Transfer<br>Efficiency    | VCTE              | 0.99999 |      | n/a  |                    | Design                |                                       |       |      |

| Photodiode Dark Current                       | lpd               | n/a     | 40   | 350  | e/p/s              | Die                   |                                       |       |      |

| Photodiode Dark Current                       | lpd               | n/a     | 0.01 | 0.1  | nA/cm²             | Die                   |                                       |       |      |

| Vertical CCD Dark Current                     | lvd               | n/a     | 400  | 1711 | e/p/s              | Die                   |                                       |       |      |

| Vertical CCD Dark Current                     | lvd               | n/a     | 0.12 | 0.5  | nA/cm <sup>2</sup> | Die                   |                                       |       |      |

| Image Lag                                     | Lag               | n/a     | <10  | 50   | e⁻                 | Design                |                                       |       |      |

| Antiblooming Factor                           | Xab               | 100     | 300  | n/a  |                    |                       |                                       |       |      |

| Vertical Smear                                | Smr               | n/a     | -80  | -75  | dB                 |                       |                                       |       |      |

| Total Noise                                   | n <sub>e-T</sub>  |         | 12   |      | e <sup>-</sup> rms | Design                |                                       | 4     |      |

| Total Noise                                   | n <sub>e-T</sub>  |         | 25   |      | e <sup>-</sup> rms | Design                |                                       | 5     |      |

| Dynamic Range                                 | DR                |         | 60   |      | dB                 | Design                |                                       | 5, 6  |      |

| Output Amplifier DC Offset                    | $V_{\rm odc}$     | 4       | 8.5  | 14   | V                  | Die                   |                                       |       |      |

| Output Amplifier Bandwidth                    | F <sub>-3db</sub> |         | 140  |      | MHz                | Design                |                                       |       |      |

| Output Amplifier Impedance                    | R <sub>out</sub>  | 100     | 130  | 200  | Ohms               | Die                   |                                       |       |      |

| Output Amplifier Sensitivity                  | ΔV/ΔΝ             |         | 31   |      | μV/e⁻              | Design                |                                       |       |      |

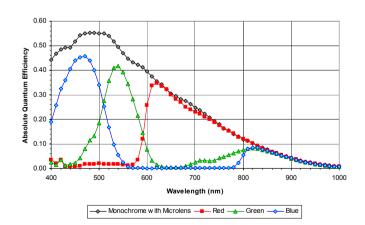

#### KAI-4021M

| Description                           | Symbol     | Min. | Nom. | Max. | Units | Samp-<br>ling<br>Plan | Tempera-<br>ture<br>Tested At<br>(°C) | Notes | Test |

|---------------------------------------|------------|------|------|------|-------|-----------------------|---------------------------------------|-------|------|

| Peak Quantum<br>Efficiency            | $QE_{max}$ | 45   | 55   | n/a  | %     | Design                |                                       |       |      |

| Peak Quantum<br>Efficiency Wavelength | λQE        | XXX  | 500  | n/a  | nm    | Design                |                                       |       |      |

### KAI-4021CM

| Description                                 |                      | Symbol            | Min. | Nom.              | Max.              | Units | Samp-<br>ling<br>Plan | Tempera-<br>ture<br>Tested At<br>(°C) | Notes | Test |

|---------------------------------------------|----------------------|-------------------|------|-------------------|-------------------|-------|-----------------------|---------------------------------------|-------|------|

| Peak<br>Quantum<br>Efficiency               | Blue<br>Green<br>Red | QE <sub>max</sub> |      | 45<br>42<br>35    | n/a<br>n/a<br>n/a | %     | Design                |                                       |       |      |

| Peak<br>Quantum<br>Efficiency<br>Wavelength | Blue<br>Green<br>Red | λQE               |      | 470<br>540<br>620 | n/a<br>n/a<br>n/a | nm    | Design                |                                       |       |      |

n/a: not applicable

### Notes:

- 1. Per color.

- Value is over the range of 10% to 90% of photodiode saturation.

- 3. Value is for the sensor operated without binning

- 4. Includes system electronics noise, dark pattern noise and dark current shot noise at 20 MHz.

5. Includes system electronics noise, dark pattern noise and dark current shot noise at 40 MHz.

- Uses 20LOG(PNe/ n<sub>e-T</sub>)

### **Defect Definitions**

| Description                            | Definition                                                                                                   | Maximum | Temperature(s)<br>tested at (°C) | Notes | Test |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------|---------|----------------------------------|-------|------|

| Major dark<br>field defective<br>pixel | Defect >= 148 mV                                                                                             | 40      | 27, 40                           | 1     | 6    |

| Major bright field defective pixel     | Defect >= 10 %                                                                                               | 40      | 27, 40                           | 1     | 7    |

| Minor dark<br>field defective<br>pixel | Defect >= 76 mV                                                                                              | 400     | 27, 40                           |       | 6    |

| Dead pixel                             | Defect >= 80 %                                                                                               | 5       | 27, 40                           | 1     | 7    |

| Saturated pixel                        | Defect >= 340 mV                                                                                             | 10      | 27, 40                           | 1     | 6    |

| Cluster defect                         | A group of 2 to 10 contiguous major<br>defective pixels, but no more than 2<br>adjacent defects horizontally | 8       | 27, 40                           | 1     |      |

| Column<br>defect                       | A group of more than 10 contiguous<br>major defective pixels along a single<br>column                        | 0       | 27, 40                           | 1     |      |

#### Notes:

## Defect Map

The defect map supplied with each sensor is based upon testing at an ambient (27°C) temperature. Minor point defects are not included in the defect map. All defective pixels are reference to pixel 1,1 in the defect maps.

<sup>1.</sup> There will be at least two non-defective pixels separating any two major defective pixels.

### Quantum Efficiency

### Monochrome Quantum Efficiency

with microlens

Figure 10: Monochrome Quantum Efficiency

### Color Quantum Efficiency

with microlens

Figure 11: Color Quantum Efficiency

## Ultraviolet (UV) Quantum Efficiency

without microlens

Figure 12: Ultraviolet Quantum Efficiency

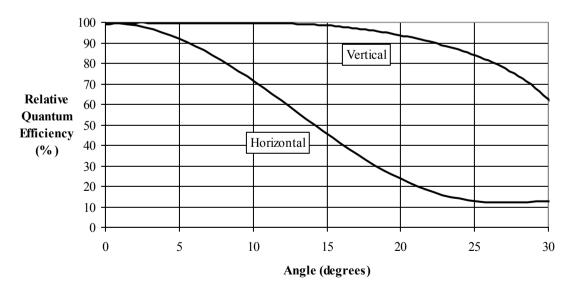

## **Angular Quantum Efficiency**

For the curves marked "Horizontal", the incident light angle is varied in a plane parallel to the HCCD. For the curves marked "Vertical", the incident light angle is varied in a plane parallel to the VCCD.

monochrome with microlens

Figure 13: Angular Quantum Efficiency

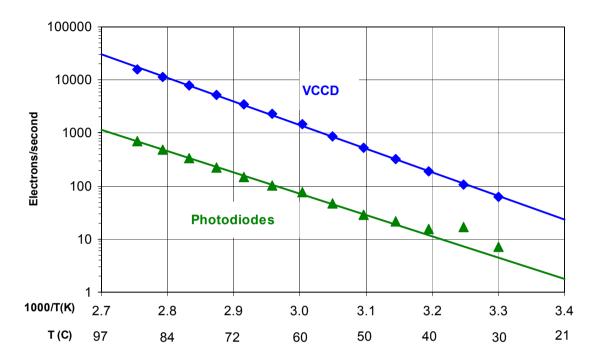

## Dark Current versus Temperature

Figure 14: Dark Current versus Temperature

## **TEST DEFINITIONS**

### TEST REGIONS OF INTEREST

Active Area ROI: Pixel 1, 1 to Pixel 2048,2048 Center 100 by 100 ROI: Pixel 974,974 to Pixel 1073,1073

Only the active pixels are used for performance and defect tests.

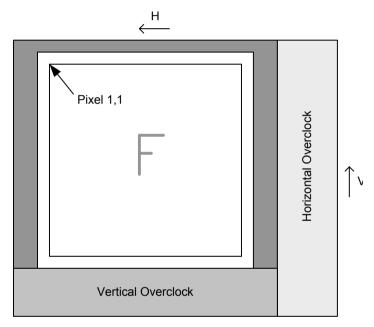

## **OVERCLOCKING**

The test system timing is configured such that the sensor is overclocked in both the vertical and horizontal directions. See Figure 15 for a pictorial representation of the regions.

Figure 15: Overclock Regions of Interest

### **TESTS**

### 1. Dark Field Center Non-Uniformity

This test is performed under dark field conditions. Only the center 100 by 100 pixels of the sensor are used for this test - pixel (974,974) to pixel (1073,1073).

Dark Field Center Non-Uniformity = Standard Deviation of center 100 by 100 pixels in mV

Units: mV rms

#### 2. Dark Field Global Non-Uniformity

This test is performed under dark field conditions. The sensor is partitioned into 256 sub regions of interest, each of which is 128 by 128 pixels in size. The average signal level of each of the 256 sub regions of interest is calculated. The signal level of each of the sub regions of interest is calculated using the following formula:

Signal of ROI[i] = (ROI Average in ADU – Horizontal overclock average in ADU) \* mV per count. Where i = 1 to 256. During this calculation on the 256 sub regions of interest, the maximum and minimum signal levels are found.

The dark field global non-uniformity is then calculated as the maximum signal found minus the minimum signal level found.

Units: mVpp (millivolts peak to peak)

#### 3. Global Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 868 mV). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 1240 mV. Global non-uniformity is defined as

Global Non - Uniformity =

$$100 * \left( \frac{\text{Active Area Standard Deviation}}{\text{Active Area Signal}} \right)$$

Units: %rms

Active Area Signal = Active Area Average - Horizontal Overclock Average

#### 4. Global Peak to Peak Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 868 mV). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 1240 mV. The sensor is partitioned into 256 sub regions of interest, each of which is 128 by 128 pixels in size. The average signal level of each of the 256 sub regions of interest (ROI) is calculated. The signal level of each of the sub regions of interest is calculated using the following formula:

A[i] = (ROI Average – Horizontal Overclock Average)

Where i = 1 to 256. During this calculation on the 256 sub regions of interest, the maximum and minimum average signal levels are found.

The global peak to peak non-uniformity is then calculated as:

$$\begin{aligned} & \text{Global Non - Uniformity} = 100* \frac{A[i] \, \text{Maximum Signal - A[i] Minimum Signal}}{\text{Active Area Signal}} \quad \text{Units: \%pp} \\ & \text{Active Area Signal} \quad \text{Active Area Average - Horizontal Overclock Average} \end{aligned}$$

#### 5. Center Non-Uniformity

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 868 mV). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 1240 mV. Defects are excluded for the calculation of this test. This test is performed on the center 100 by 100 pixels (See Test Regions of Interest) of the sensor. Center non-uniformity is defined as:

Center ROI Non - Uniformity =

$$100 * \left( \frac{\text{Center ROI Standard Deviation}}{\text{Center ROI Signal}} \right)$$

Units: %rms

#### 6. Dark field defect test

This test is performed under dark field conditions. The sensor is partitioned into 256 sub regions of interest, each of which is 128 by 128 pixels in size. In each region of interest, the median value of all pixels is found. For each region of interest, a pixel is marked defective if it is greater than or equal to the median value of that region of interest plus the defect threshold specified in "Defect Definitions" section.

### 7. Bright field defect test

This test is performed with the imager illuminated to a level such that the output is at 70% of saturation (approximately 28,000 electrons). Prior to this test being performed the substrate voltage has been set such that the charge capacity of the sensor is 40,000 electrons. The average signal level of all active pixels is found. The bright and dark thresholds are set as:

Dark defect threshold = Active Area Signal \* threshold Bright defect threshold = Active Area Signal \* threshold

The sensor is then partitioned into 256 sub regions of interest, each of which is 128 by 128 pixels in size. In each region of interest, the average value of all pixels is found. For each region of interest, a pixel is marked defective if it is greater than or equal to the median value of that region of interest plus the bright threshold specified or if it is less than or equal to the median value of that region of interest minus the dark threshold specified.

Example for major bright field defective pixels:

- Average value of all active pixels is found to be 868 mV (28,000 electrons).

- Dark defect threshold: 868mV \* 15% = 130.2 mV

- Bright defect threshold: 868mV \* 15% = 130.2 mV

- Region of interest #1 selected. This region of interest is pixels 1,1 to pixels 128,128.

- Median of this region of interest is found to be 868 mV.

- Any pixel in this region of interest that is >= (868+130.2 mV) 998.2 mV in intensity will be marked defective.

- Any pixel in this region of interest that is <= (868-130.2 mV) 737.8 mV in intensity will be marked defective.

- All remaining 255 sub-regions of interest are analyzed for defective pixels in the same manner.

## **OPERATION**

### MAXIMUM RATINGS

Absolute maximum rating is defined as a level or condition that should not be exceeded at any time per the description. If the level or the condition is exceeded, the device will be degraded and may be damaged.

| Description           | Symbol | Minimum | Maximum | Units | Notes |

|-----------------------|--------|---------|---------|-------|-------|

| Operating Temperature | T      | -50     | 70      | °C    | 1     |

| Humidity              | RH     | 5       | 90      | %     | 2     |

| Output Bias Current   | lout   | 0.0     | 10      | mA    | 3     |

| Off-chip Load         | Cı     |         | 10      | pF    | 4     |

#### Notes:

- 1. Noise performance will degrade at higher temperatures.

- 2. T=25°C. Excessive humidity will degrade MTTF.

- 3. Each output. See Figure 16: Output Amplifier. Note that the current bias affects the amplifier bandwidth.

- 4. With total output load capacitance of CL = 10pF between the outputs and AC ground.

- 5. Absolute maximum rating is defined as a level or condition that should not be exceeded at any time per the description. If the level or the condition is exceeded, the device will be degraded and may be damaged.

### MAXIMUM VOLTAGE RATINGS BETWEEN PINS

| Description                                               | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------------|---------|---------|-------|-------|

| RL, RR, H1S, H2S, H1BL, H2BL, H1BR, H2BR, OGR, OGL to ESD | 0       | 17      | ٧     |       |

| Pin to Pin with ESD Protection                            | -17     | 17      | V     | 1     |

| VDDL, VDDR to GND                                         | 0       | 25      | V     |       |

#### Notes:

1. Pins with ESD protection are: RL, RR, H1S, H2S, H1BL, H2BL, H1BR, H2BR, OGL, and OGR.

### DC BIAS OPERATING CONDITIONS

| Description             | Symbol | Minimum | Nominal | Maximum | Units | Maximum DC<br>Current (mA) | Notes |

|-------------------------|--------|---------|---------|---------|-------|----------------------------|-------|

| Output Gate             | OG     | -3.0    | -2.0    | -1.5    | V     | 1 μΑ                       | 4, 5  |

| Reset Drain             | RD     | 11.5    | 12.0    | 12.5    | V     | 1 μΑ                       | 4     |

| Output Amplifier Supply | VDD    | 14.5    | 15.0    | 15.5    | V     | 1 mA                       | 3     |

| Ground                  | GND    | 0.0     | 0.0     | 0.0     | V     |                            |       |

| Substrate               | SUB    | 8.0     | Vab     | 17.0    | V     |                            | 1     |

| ESD Protection          | ESD    | -9.5    | -9.0    | -8.0    | V     |                            | 2     |

| Output Bias Current     | lout   | 0.0     | 5.0     | 10.0    | mA    |                            | 6     |

#### Notes:

- 1. The operating value of the substrate voltage, Vab, will be marked on the shipping container for each device. The value Vab is set such that the photodiode charge capacity is 40,000 electrons.

- 2. VESD must be equal to FDL and more negative than H1L, H2L and RL during sensors operation AND during camera power turn on.

- 3. One output, unloaded. The maximum DC current is for one output unloaded and is shown as Iss in Figure 16. This is the maximum current that the first two stages of one output amplifier will draw. This value is with Vout disconnected.

- 4. May be changed in future versions.

- 5. Output gate voltage level must be set to -3V for 40,000 80,000 electrons output in summed interlaced or binning modes.

- 6. One output.

Figure 16: Output Amplifier

## AC OPERATING CONDITIONS

### **Clock Levels**

| Description                  | Symbol   | Minimum | Nominal | Maximum | Units | Notes |

|------------------------------|----------|---------|---------|---------|-------|-------|

| Vertical CCD Clock High      | V2H      | 8.5     | 9.0     | 9.5     | V     |       |

| Vertical CCD Clocks Midlevel | V1M, V2M | -0.5    | 0.0     | 0.2     | V     |       |

| Vertical CCD Clocks Low      | V1L, V2L | -9.5    | -9.0    | -8.5    | V     |       |

| Horizontal CCD Clocks High   | H1H, H2H | 0.0     | 0.5     | 1.0     | V     |       |

| Horizontal CCD Clocks Low    | H1L, H2L | -5.0    | -4.5    | -4.0    | V     |       |

| Reset Clock Amplitude        | RH       |         | 5.0     |         | V     | 1     |

| Reset Clock Low              | RL       | -3.5    | -3.0    | -2.5    | V     |       |

| Electronic Shutter Voltage   | Vshutter | 44      | 48      | 52      | V     |       |

| Fast Dump High               | FDH      | 4       | 5       | 5       | V     |       |

| Fast Dump Low                | FDL      | -9.5    | -9      | -8      | V     |       |

Notes:

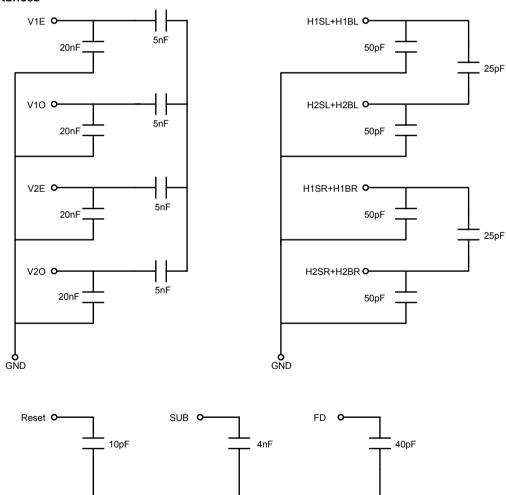

## **Clock Line Capacitances**

Figure 17: Clock Line Capacitances

**O** GND

**O** GND

<sup>1.</sup> Reset amplitude must be set to 7.0 V for 40,000 – 80,000 electrons output in summed interlaced or binning modes.

## TIMING REQUIREMENTS

| Description                   | Symbol            | Minimum | Nominal | Maximum | Units | Notes |

|-------------------------------|-------------------|---------|---------|---------|-------|-------|

| HCCD Delay                    | T <sub>HD</sub>   | 1.3     | 1.5     | 10.0    | μs    |       |

| VCCD Transfer time            | T <sub>VCCD</sub> | 1.3     | 1.5     | 20.0    | μs    |       |

| Photodiode Transfer time      | T <sub>V3rd</sub> | 3.0     | 5.0     | 15.0    | μs    |       |

| VCCD Pedestal time            | T <sub>3P</sub>   | 50.0    | 60.0    | 80.0    | μs    |       |

| VCCD Delay                    | T <sub>3D</sub>   | 10.0    | 20.0    | 80.0    | μs    |       |

| Reset Pulse time              | T <sub>R</sub>    | 2.5     | 5.0     |         | ns    |       |

| Shutter Pulse time            | Ts                | 3.0     | 4.0     | 10.0    | μs    |       |

| Shutter Pulse delay           | $T_{SD}$          | 1.0     | 1.5     | 10.0    | μs    |       |

| HCCD Clock Period             | T <sub>H</sub>    | 25.0    | 50.0    | 200.0   | ns    | 1     |

| VCCD rise/fall time           | T <sub>VR</sub>   | 0.0     | 0.1     | 1.0     | μs    |       |

| Fast Dump Gate delay          | $T_{FD}$          | 0.5     |         |         | μs    |       |

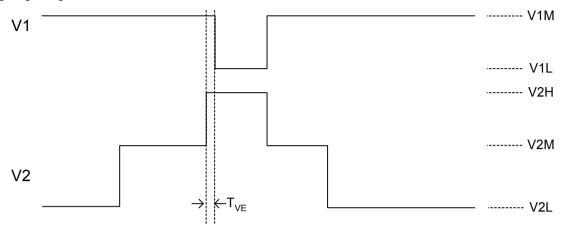

| Vertical Clock Edge Alignment | T <sub>VE</sub>   | 0.0     |         | 100.0   | ns    |       |

### Notes:

<sup>1.</sup> For operation at the minimum HCCD clock period (40MHz), the substrate voltage will need to be raised to limit the signal at the output to 20,000 electrons.

### TIMING MODES

### **Progressive Scan**

In progressive scan read out every pixel in the image sensor is read out simultaneously. Each charge packet is transferred from the photodiode to the neighboring vertical CCD shift register simultaneously. The maximum useful signal output is limited by the photodiode charge capacity to 40,000 electrons.

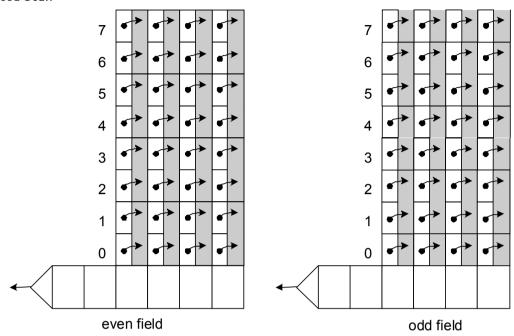

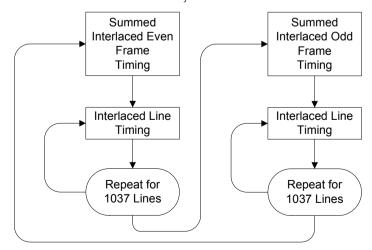

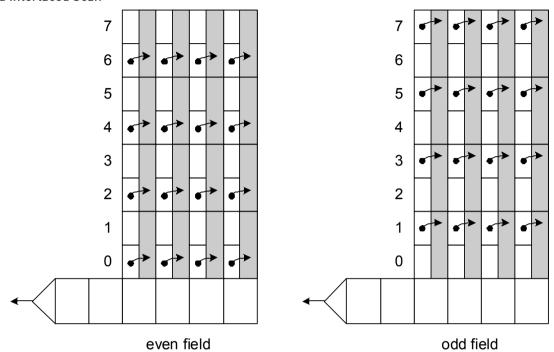

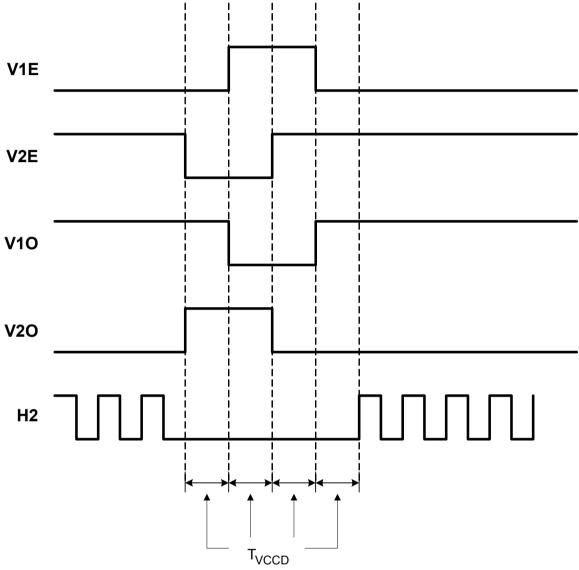

#### Summed Interlaced Scan

In the summed interlaced scan read out mode, charge from two photodiodes are summed together inside the vertical CCD. The clocking of the VCCD is such that one pixel occupies the space equivalent to two pixels in the progressive scan mode. This allows the VCCD to hold twice as many electrons as in progressive scan mode. Now the maximum useful signal is limited by the charge capacity of two photodiodes at 80,000 electrons. If only one field is read out of the image sensor the apparent vertical resolution will be 1024 rows instead of the 2048 rows in progressive scan (equivalent to binning). To recover the full resolution of the image sensor two fields, even and odd, are read out. In the even field rows 0+1, 2+3, 4+5, ... are summed together. In the odd field rows 1+2, 3+4, 5+6, ... are summed together.

The modulation transfer function (MTF) of the summed interlaced scan mode is less in the vertical direction than the progressive scan. But the dynamic range is twice that of progressive scan. The vertical MTF is better than a simple binning operation. In this mode the VCCD needs to be clocked for only 1037 rows to read out each field.

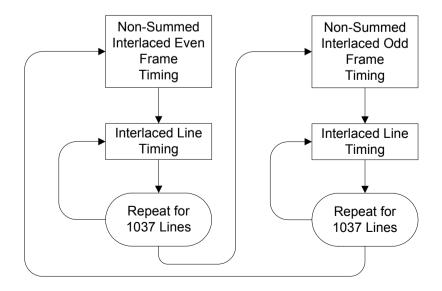

#### Non-Summed Interlaced Scan

In the non-summed interlaced scan mode only half the photodiode are read out in each field. In the even field rows 0, 2, 4, ... are transferred to the VCCD. When the charge packet is transferred from a photodiode is occupies the equivalent of two rows in progressive scan mode. This allows the VCCD to hold twice as much charge a progressive scan mode. However, since only one photodiode for each row is transferred to the VCCD the maximum usable signal is still only 40,000 electrons. The large extra capacity of the VCCD causes the anti-blooming protection to be increased dramatically compared to the progressive scan. The vertical MTF is the same between the non-summed interlaced scan and progressive scan. There will be motion related artifacts in the images read out in the interlaced modes because the two fields are acquired at different times.

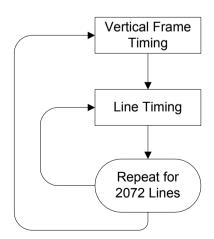

## FRAME TIMING

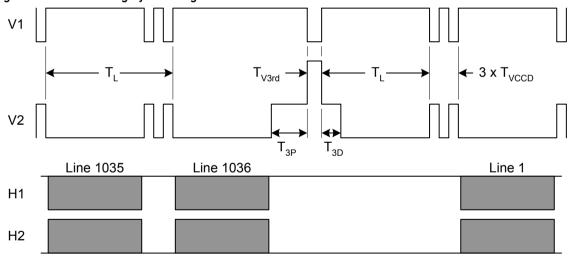

# Frame Timing without Binning - Progressive Scam

Figure 18: Framing Timing without Binning

## Frame Timing for Vertical Binning by 2 - Progressive Scan

Figure 19: Frame Timing for Vertical Binning by 2

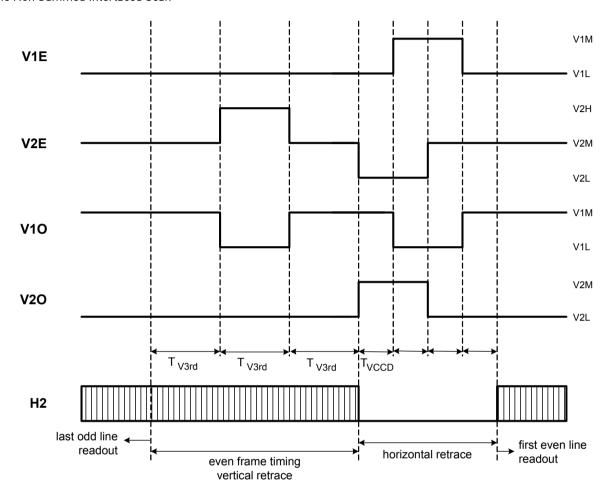

## Frame Timing Non-Summed Interlaced Scan

Even Frame Non Summed Interlaced Scan

Figure 20: Non-Summed Interlaced Scan Even Frame Timing

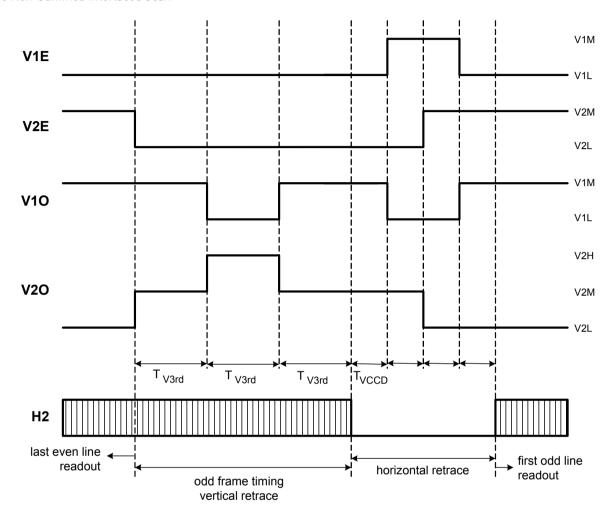

### Odd Frame Non-Summed Interlaced Scan

Figure 21: Non-Summed Interlaced Scan Odd Frame Timing

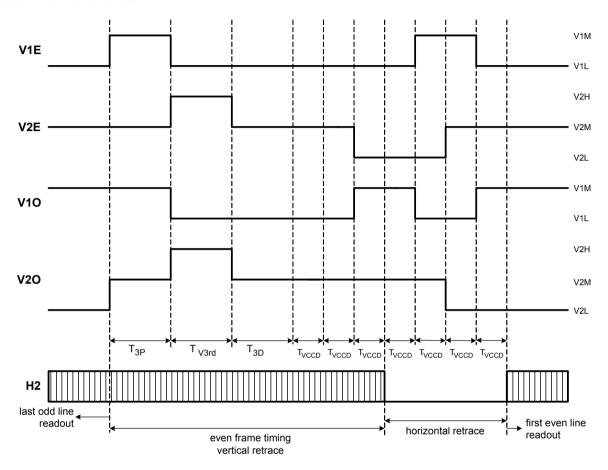

## Frame Timing Summed Interlaced Scan

Even Frame Summed Interlaced Scan

Figure 22: Summed Interlaced Scan Even Frame Timing

### Odd Frame Summed Interlaced Scan

Figure 23: Summed Interlaced Scan Odd Frame Timing

# Frame Timing Edge Alignment

Figure 24: Frame Timing Edge Alignment

## **LINE TIMING**

# Line Timing Single Output - Progressive Scan

Figure 25: Line Timing Single Output

# Line Timing Dual Output - Progressive Scan

Figure 26: Line Timing Dual Output

# Line Timing Vertical Binning by 2 - Progressive Scan

Figure 27: Line Timing Vertical Binning by 2

# Line Timing Detail - Progressive Scan

Figure 28: Line Timing Detail

# Line Timing Binning by 2 Detail - Progressive Scan

Figure 29: Line Timing by 2 Detail

# Line Timing Interlaced Modes

Figure 30: Line Timing Interlaced Modes

# Line Timing Edge Alignment Applies to all modes.

Figure 31: Line Timing Edge Alignment

# **PIXEL TIMING**

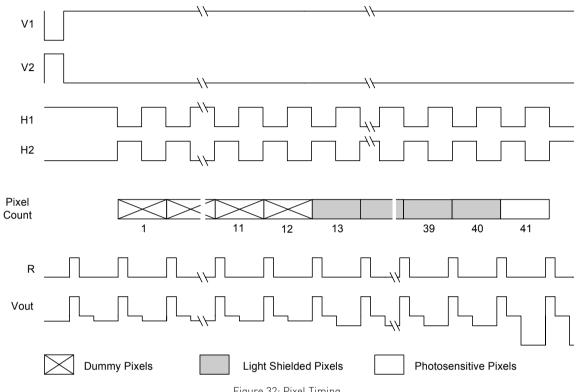

Figure 32: Pixel Timing

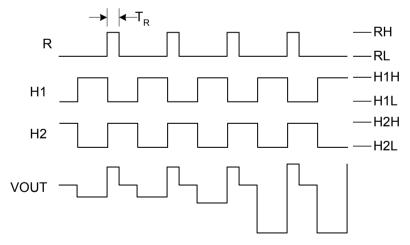

# Pixel Timing Detail

Figure 33: Pixel Timing Detail

# FAST LINE DUMP TIMING

Figure 34: Fast Line Dump Timing

# **ELECTRONIC SHUTTER**

# **Electronic Shutter Line Timing**

Figure 35: Electronic Shutter Line Timing

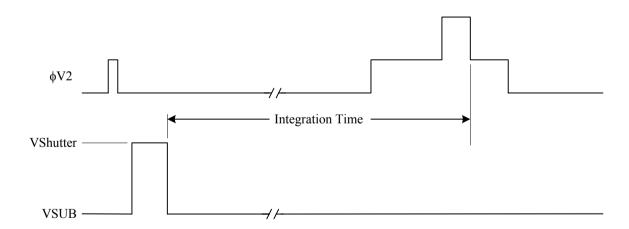

# **Electronic Shutter – Integration Time Definition**

Figure 36: Integration Time Definition

#### **Electronic Shutter Description**

The voltage on the substrate (SUB) determines the charge capacity of the photodiodes. When SUB is 8 volts the photodiodes will be at their maximum charge capacity. Increasing VSUB above 8 volts decreases the charge capacity of the photodiodes until 48 volts when the photodiodes have a charge capacity of zero electrons. Therefore, a short pulse on SUB, with a peak amplitude greater than 48 volts, empties all photodiodes and provides the electronic shuttering action.

It may appear the optimal substrate voltage setting is 8 volts to obtain the maximum charge capacity and dynamic range. While setting VSUB to 8 volts will provide the maximum dynamic range, it will also provide the minimum antiblooming protection.

The KAI-4021 VCCD has a charge capacity of 60,000 electrons (60 ke<sup>-</sup>). If the SUB voltage is set such that the photodiode holds more than 60 ke<sup>-</sup>, then when the charge is transferred from a full photodiode to VCCD, the VCCD will overflow. This overflow condition manifests itself in the image by making bright spots appear elongated in the vertical direction. The size increase of a bright spot is called blooming when the spot doubles in size. The blooming can be eliminated by increasing the voltage on SUB to lower the charge capacity of the photodiode. This ensures the VCCD charge capacity is greater than the photodiode capacity. There are cases where an extremely bright spot will still cause blooming in the VCCD. Normally, when the photodiode is full, any additional electrons generated by photons will spill out of the photodiode. The excess electrons are drained harmlessly out to the substrate. There is a maximum rate at which the electrons can be drained to the substrate. If that maximum rate is exceeded, (for example, by a very bright light source) then it is possible for the total amount of charge in the photodiode to exceed the VCCD capacity. This results in blooming. The amount of antiblooming protection also decreases when the integration time is decreased. There is a compromise between photodiode dynamic range (controlled by VSUB) and the amount of antiblooming protection. A low VSUB voltage provides the maximum dynamic range and minimum (or no) antiblooming protection. A high VSUB voltage provides lower dynamic range and maximum antiblooming protection. The optimal setting of VSUB is written on the container in which each KAI-4021 is shipped. The given VSUB voltage for each sensor is selected to provide antiblooming protection for bright spots at least 100 times saturation, while maintaining at least 40ke<sup>-</sup> of dynamic range.

The electronic shutter provides a method of precisely controlling the image exposure time without any mechanical components. If an integration time of  $T_{\text{INT}}$  is desired, then the substrate voltage of the sensor is pulsed to at least 40 volts  $T_{\text{INT}}$  seconds before the photodiode to VCCD transfer pulse on V2. Use of the electronic shutter does not have to wait until the previously acquired image has been completely read out of the VCCD.

# LARGE SIGNAL OUTPUT

When the image sensor is operated in the binned or summed interlaced modes there will be more than 20,000 electrons in the output signal. The image sensor is designed with a 31µV/e charge to voltage conversion on the output. This means a full signal of 20,000 electrons will produce a 640 mV change on the output amplifier. The output amplifier was designed to handle an output swing of 640 mV at a pixel rate of 40 MHz. If 40,000 electron charge packets are generated in the binned or summed interlaced modes then the output amplifier output will have to swing 1280 mV. The output amplifier does not have enough bandwidth (slew rate) to handle 1280 mV at 40 MHz. Hence, the pixel rate will have to be reduced to 20 MHz if the full dynamic range of 40,000 electrons is desired.

The charge handling capacity of the output amplifier is also set by the reset clock voltage levels. The reset clock driver circuit is very simple if an amplitude of 5V is used. But the 5V amplitude restricts the output amplifier charge capacity to 20,000 electrons. If the full dynamic range of 40,000 electrons is desired then the reset clock amplitude will have to be increased to 7V.

If you only want a maximum signal of 20,000 electrons in binned or summed interlaced modes, then a 40 MHz pixel rate with a 5V reset clock may be used. The output of the amplifier will be unpredictable above 20,000 electrons so be sure to set the maximum input signal level of your analog to digital converter to the equivalent of 20,000 electrons (640mV).

#### STORAGE AND HANDLING

#### Storage Conditions

| Description            | Symbol          | Minimum | Maximum | Units | Notes |

|------------------------|-----------------|---------|---------|-------|-------|

| Storage<br>Temperature | T <sub>ST</sub> | -55     | 80      | °C    | 1     |

| Humidity               | RH              | 5       | 90      | %     | 2     |

#### Notes:

- 1. Long-term exposure toward the maximum temperature will accelerate color filter degradation.

- 2. T=25°C. Excessive humidity will degrade MTTF.

#### ESD

- This device contains limited protection against Electrostatic Discharge (ESD). CCD image sensors can be damaged by electrostatic discharge. Failure to do so may alter device performance and reliability.

- 2. Devices should be handled in accordance with strict ESD procedures for Class 0 (<250V per JESD22 Human Body Model test), or Class A (<200V JESD22 Machine Model test) devices.

- Devices are shipped in static-safe containers and should only be handled at static-safe workstations.

- 3. See Application Note MTD/PS-0224 "Electrostatic Discharge Control for Image Sensors" for proper handling and grounding procedures. This application note also contains recommendations for workplace modifications for the minimization of electrostatic discharge.

- 4. Store devices in containers made of electroconductive materials.

#### Cover Glass Care and Cleanliness

- 1. The cover glass is highly susceptible to particles and other contamination. Perform all assembly operations in a clean environment.

- 2. Touching the cover glass must be avoided

- 3. Improper cleaning of the cover glass may damage these devices. Refer to Application Note MTD/PS-0237 "Cover Glass Cleaning for Image Sensors"

#### Environmental Exposure

- 1. Do not expose to strong sun light for long periods of time. The color filters and/or microlenses may become discolored. Long time exposures to a static high contrast scene should be avoided. The image sensor may become discolored and localized changes in response may occur from color filter/microlens aging.

- 2. Exposure to temperatures exceeding the absolute maximum levels should be avoided for storage and operation. Failure to do so may alter device performance and reliability.

- 3. Avoid sudden temperature changes.

- 4. Exposure to excessive humidity will affect device characteristics and should be avoided. Failure to do so may alter device performance and reliability.

- 5. Avoid storage of the product in the presence of dust or corrosive agents or gases.

- Long-term storage should be avoided. Deterioration of lead solderability may occur. It is advised that the solderability of the device leads be re-inspected after an extended period of storage, over one year.

#### Soldering Recommendations

- 1. The soldering iron tip temperature is not to exceed 370°C. Failure to do so may alter device performance and reliability.

- 2. Flow soldering method is not recommended. Solder dipping can cause damage to the glass and harm the imaging capability of the device. Recommended method is by partial heating. Kodak recommends the use of a grounded 30W soldering iron. Heat each pin for less than 2 seconds duration.

## **MECHANICAL DRAWINGS**

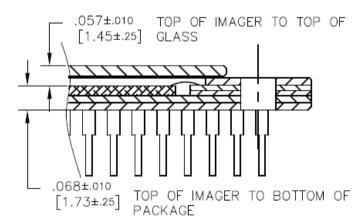

## **PACKAGE**

Figure 37: Package Drawing

The cover glass is manually placed and aligned.

## DIE TO PACKAGE ALIGNMENT

#### NOTES:

- 1. CENTER OF IMAGE IS OFFSET FROM CENTER OF PACKAGE

BY COORDINATES (-.157, 0.000)mm NOMINAL.

- 2. DIE IS ALIGNED IN WITHIN +/- 1 DEGREES OF ANY PACKAGE CAVITY EDGE.

Figure 38: Die to Package Alignment

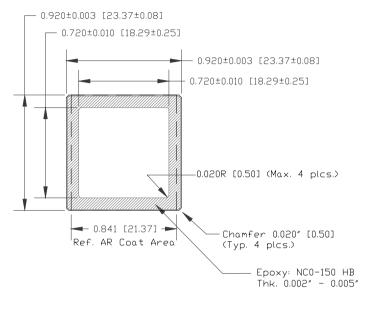

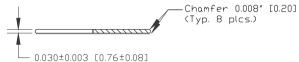

# **GLASS**

#### NOTES:

- Multi-Layer Anti-Reflective Coating on 2 sides: Double Sided Reflectance:

- Range (nm)

- 420 435 nm < 2.0%

- 435 630 nm < 0.8%

- 630 680 nm < 2.0%

- 2. Dust, Scratch specification 10 microns max.

- 3. Substrate Schott D-263 or Equivalent

- 4. Epoxy: NC□-150HB

- Thickness: 0.002" 0.005"

DIMENSIONS UNITS: INCH [MM]

TOLERANCE: UNLESS OTHERWISE SPECIFIED CERAMIC: + 1% NO LESS THAN 0.004" L/F: + 1% NO MORE THAN 0.004"

Figure 39: Glass Drawing

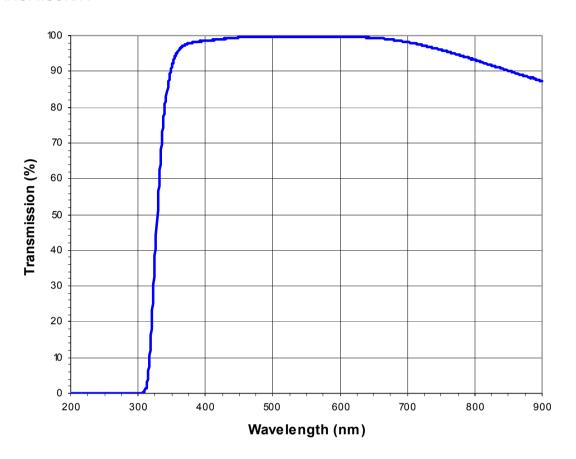

# **GLASS TRANSMISSION**

Figure 40: Glass Transmission

### **QUALITY ASSURANCE AND RELIABILITY**

Quality Strategy: All image sensors will conform to the specifications stated in this document. This will be accomplished through a combination of statistical process control and inspection at key points of the production process. Typical specification limits are not guaranteed but provided as a design target. For further information refer to ISS Application Note MTD/PS-0292, Quality and Reliability.

Replacement: All devices are warranted against failure in accordance with the terms of Terms of Sale. This does not include failure due to mechanical and electrical causes defined as the liability of the customer below.

Liability of the Supplier: A reject is defined as an image sensor that does not meet all of the specifications in this document upon receipt by the customer.

Liability of the Customer: Damage from mechanical (scratches or breakage), electrostatic discharge (ESD) damage, or other electrical misuse of the device beyond the stated absolute maximum ratings, which occurred after receipt of the sensor by the customer, shall be the responsibility of the customer.

**ESD Precautions:** Devices are shipped in static-safe containers and should only be handled at static-safe workstations. See ISS Application Note MTD/PS-0224, Electrostatic Discharge Control, for handling recommendations.

Reliability: Information concerning the quality assurance and reliability testing procedures and results are available from the Image Sensor Solutions and can be supplied upon request. For further information refer to ISS Application Note MTD/PS-0292, Quality and Reliability.

**Test Data Retention:** Image sensors shall have an identifying number traceable to a test data file. Test data shall be kept for a period of 2 years after date of delivery.

**Mechanical:** The device assembly drawing is provided as a reference. The device will conform to the published package tolerances.

## ORDERING INFORMATION

Available Part Configurations

| Туре       | Description              | Glass Configuration | Marking Code     |  |

|------------|--------------------------|---------------------|------------------|--|

| KAI-4021   | Monochrome               | Taped               | KAI-4021<br>SN   |  |

| KAI-4021M  | Monochrome with Lenslets | Sealed or Taped     | KAI-4021M<br>SN  |  |

| KAI-4021CM | Color with Lenslets      | Sealed or Taped     | KAI-4021CM<br>SN |  |

Please contact Image Sensor Solutions for available part numbers.

## Address all inquiries and purchase orders to:

Image Sensor Solutions Eastman Kodak Company Rochester, New York 14650-2010

Phone: (585) 722-4385 Fax: (585) 477-4947 E-mail: imagers@kodak.com

Kodak reserves the right to change any information contained herein without notice. All information furnished by Kodak is believed to be accurate.

#### WARNING: LIFE SUPPORT APPLICATIONS POLICY

Kodak image sensors are not authorized for and should not be used within Life Support Systems without the specific written consent of the Eastman Kodak Company. Product warranty is limited to replacement of defective components and does not cover injury or property or other consequential damages.

# **REVISION CHANGES**

| Revision<br>Number | Description of Changes                                                                                                                                                                                                                                            |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                | Initial formal release                                                                                                                                                                                                                                            |

| 1.1                | <ul> <li>Page 26 – Removed caution for cover glass protective tape. The use of the protective tape has been discontinued.</li> <li>Page 48 – Removed note under Cover Glass Care and Cleanliness section that referred to cover glass protective tape.</li> </ul> |

| 2.0                | <ul> <li>Updated format</li> <li>Pages 48 and 49 – Updated package drawings.</li> </ul>                                                                                                                                                                           |

This page intentionally left blank.